### **1**

## System Security in Embedded Systems based on Hardware Support

#### Adyanata Lubis<sup>1</sup>, B. Herawan Hayadi<sup>2</sup>

<sup>1</sup>STIKIP Rokania, Riau, Indonesia.

<sup>2</sup> Universitas Ibnu Sina, Batam, Indonesia.

E-mail: adyanata@gmail.com<sup>1</sup>, b.herawan.hayadi@gmail.com<sup>2</sup>

# Article Info ABSTRACT Article history: The natural impediments of implanted frameworks make them especially defenseless against assaults. We have built up an equipment screen that works in corresponding to the implanted processor and distinguishes any

defenseless against assaults. We have built up an equipment screen that works in corresponding to the implanted processor and distinguishes any assault that makes the inserted processor veer off from its initially modified conduct. We investigate a few unique attributes that can be utilized for checking and quantitative tradeoffs between these methodologies. Our outcomes provide that the new projected hash-based observing example can identify assaults inside one guidance series at lesser memory necessities than customary methodologies that utilization control-stream data.

#### Keywords:

Embedded system security Hardware Monitor Operating System Attack

Revised Oct 23, 2024

Accepted Nov 12, 2024

#### Corresponding Author:

Adyanata Lubis, STIKIP Rokania, Riau, Indonesia.

#### 1. INTRODUCTION

A key component of the expanding Internet of Things (IoT) are embedded processing systems, just as broad organize frameworks, keen wellbeing frameworks, and numerous other application areas. These frameworks are commonly associated with one another furthermore, a distributed computing framework through the web. The estimation of information on these frameworks, their admittance to physical conditions, and the potential pulverization that can be originated by them create these gadgets alluring focuses for aggressors. Two perspectives are of specific significance in this safe setting. To start with, the implanted frameworks are associated with the Internet and subsequently powerless against far off assaults. Second, the installed frameworks commonly don't have the preparing limit or force spending plan to run programming based safeguard mechanisms, for example, infection scanners or interruption recognition frameworks, which are regularly utilized as security arrangements in-network- associated workstation and worker PCs.

Along these lines, it is basic to create guard systems for these implanted frameworks that are compelling to safeguard against assaults and that are functional to execute in an asset obliged climate. In this study, we provide equipment based observing framework that can follow every guidance that is implemented by the implanted processor and ensure on the off chance that it matches the normal conduct of the framework. To figure out what conduct is right, we break down the working framework (OS) and application doubles to make an observing diagram for each. The equipment screen can identify this divergence because, in the event that the framework is attacked, it will essentially execute instructions that are not a part of such an observing diagram. To ensure that the screen can verify the consistent execution of all instructions on the implanted network processor, our framework may adhere to the framework's components (e.g., setting switches, working framework intrusions, and so on).

This study's primary commitment is a minor safety feature that can adhere to the function's implementation and functioning framework and identify attacks at the level of a person's computer instructions without requiring the identification of any specific type of attack. Our report specifically outlines the following pledges:

- Instrument layout based observing framework that can identify any divergence in handling conduct in the operating framework or request undertakings, in any event, when brought about by already obscure assaults.

- To illustrate the viability of this approach, a prototype implementation of an equipment-based screening framework using the  $\mu$ C/OS-II working framework is performed on a change DE4 FPGA board.

- The model framework's evaluation demonstrates its ability to effectively change settings, manage intrusions, and detect attacks, all while requiring two or three hundred logical entryways and storage space equivalent to the guidance code and resulting in a negligible handling halt of six engine turns per setting change.

The rest of this work depicts the plan, activity, what's more, usage of this equipment security system for working frameworks of implanted preparing frameworks.

#### 2. LITERATURE REVIEW

The significance of security in inserted conditions, for example, in IoT, has for quite some time been recognized in scholastic exploration [1] and by government organizations [2]. Ongoing assaults on Internet framework abused weaknesses in IoT gadgets to dispatch appropriated disavowal of-administration assaults [3], which features the proceeded with the requirement for novel security arrangements in this space.

Albeit universally useful working frameworks contain an assortment of security components, inserted OS forms are restricted, and checking for installed working frameworks is obliged. A few procedures are utilized to give working framework security at run-time. Ordinary components incorporate a believed figuring base and a reference screen [4]. The product instruments authorize a security strategy and admittance to figure objects, individually. Dynamic data stream security [5] can be functioned to working frameworks to keep information from incoming paths from being utilized as guidelines or bounce objectives. Information driven methodology adds security data to capacity areas and registers to follow safety stages [6]. A later approach evaluates the usage of designs in the processor's programmed counters and series in accordance with instructions using a neural structure [7]. These boundaries reveal peculiar working framework behavior. To identify shocking changes, the Fingerprint Evident Processor [8] uses bitcoins to designate information values. These characteristics are used to identify changes to OS information.

Using a piece of equipment based observing framework to identify preparing divergence is surely not original: Monitors have been used to follow capacity and framework call successions [9], to confirm checksums over essential squares [10], and to approve execution at a for each guidance level [11]. In this work, we present a guidance-by-guidance point equipment checking approach for a complicated, communicating programming environment (i.e., several handling tasks operating on a functional framework). This kind of fine-grained checking technique has not already been shown for an all-out working framework with various assignments. Although the work in [12], [13] considers various handling assignments, it does not screen the working framework themselves, that is often the target of attacks. Coarser-grained approaches have thought about working frameworks and handling assignments, however, don't follow handling conduct at the degree of singular guidelines, which frees them up to weaknesses, for example, depicted, where assaults have been performed on system processors utilizing a couple of directions of malevolent code.

#### 3. SECURITY MODEL AND ARRANGEMENT

To give setting to our plan that we depict in the following part and assess in the next part, we quickly examine the framework design, the creation of an observation chart and the security strategy that motivates new work.

#### Checking building of graphs

The fundamental thought of equipment observing is to look at framework conduct against a brilliant marker. Here we utilize a fine-grained pointer known as a checking chart. This chart is a determinative limited machine wherein the states are the get-together directions and boundaries are the potential advances among those guidelines. It tends to be built by investigating the paired cryptogram of a function. A major test in chart development is settling circuitous control stream directions where the objective location of guidance is controlled by the substance of a record. Provider code analysis, characterization, and double function copying [14] can be used to address these principles. A brief discussion of the chart removal measure can be found in [15].

IJCM □ 3

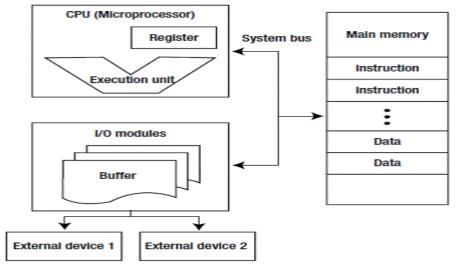

Figure 1. Representation of Embedded Hardware Monitoring

#### Framework Architecture

The framework design of our equipment observing framework has appeared in Fig. 1. The processor center information all performed guidance to the equipment screen which analyzes the guidance besides a section in the checking chart. For the situation of deviation for a normal chart crossing because of assault, a recuperation methodology is started, as talked about in part V. Such an equipment inspection method has been portrayed in literature work. We pick the per-guidance checking method projected in [16], as opposed to the per-essential square observing introduced or the framework call checking introduced to guarantee quick reaction to assaults. Additionally, we utilize the 4-cycle hash of the handled guidance for detailing depicted (as opposed to the full guidance word) to diminish memory necessities. At long last, we utilize the security methods depicted to keep an assailant from messing with the checking chart to dodge recognition.

The requirement to associate the present prepared setting (working framework or one of the many functions) with the appropriate checking setting is the test for this framework, and represents the main peculiarity above associated with work. Each program and operating system has its own observation diagram (and associated checking state), as shown in Fig. 1. At the point when the processor switches among function and working framework processing (e.g., because of setting switch, interferes, and so on), the equipment screen needs to track these dynamic changes.

#### **Model of Security**

We think that safety possessions that are connected to the integrity of depiction are important after illustrating the framework engineering and creating a checking chart. Our framework's safety requirements are:

SR1 Only code that fits inside the functioning framework or any of the requests that have been properly introduced should be executed by the framework.

SR2 Any assault that presents a vindictive code ought to be recognized and halted.

The aggressor capacities that we accept are:

AC1 An aggressor approaches the installed framework through any info/yield channel.

AC2 An assailant can mess with the application and working framework pairs stacked into the fundamental reminiscence, the preparing stack, and information memory.

In this study, we additionally expect the accompanying impediment on assailant capacities:

AC3 An aggressor can't alter the checking diagram (e.g., by utilizing the procedures from [12]).

Notwithstanding these security prerequisites, there are execution necessities, for example, low usage cost and low execution overhead, to make the framework essentially valuable.

#### 4. **DESIGN MONITORING**

This part provides the details of different aspects of the hardware design monitor.

#### **Working System Task Management**

The critical part of the checking framework is its capacity to screen equally client and working framework undertakings. The working framework (for example, a new client mission is planned), functions calling the framework, or other functions (such as the clock or outside interference) might initiate errand trading. In the initial two situations, the setting switch occurs simultaneously, implying that the guidance

after which the setting switch happens is recognized. Hence, the proper data can be given to the equipment screen preceding the function by accumulating a little bit of code to the Operating System and the functions. Be that as it may, in the last case, the setting switch can occur with no earlier notification. Setting the switch method on the equipment screen incorporates sparing the condition of the checking diagram for the code right now being carried out and changing to the chart for the following processor work. Since hinders can happen non concurrently, this entire technique ought to be done consistently and without any coordination between the fundamental processor and the equipment screen.

#### Perform multiple tasks Hardware Monitor System

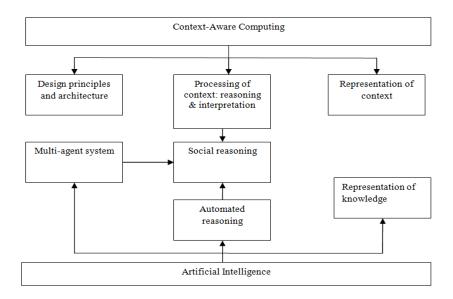

A comprehensive perspective on our observing subsystem has appeared in Fig. 2. The components of the observing framework include the following: system interfaces, which help the CPU when setting connected data is obtained; finance tables with information, used for observing schematics with an obvious client and OS undertakings; representation memory, which keeps information about state about checking diagrams; sequencing rationale, which determines the next state in the diagram; and tracking equipment, that monitors the friend processor's per-guidance activity.

Additionally, the tables track each diagram's observing status. Using a digital currency coprocessor, observing diagrams can be stacked from outer memory into a secure storage. A limited state machine restricts movement in the observation apparatus. We implemented this framework and evaluated how well it displayed on a DE4 FPGA board. The cycle ID (PID) of the most recent errand, together with the relevant diagram ID, are displayed on the equipment screen when the OS runs another errand. In the event that it is not currently occupied, the equipment screen then associates this PID with the obtained GID in the accounting tables and stacks the fitting diagram into its chart memory.

#### Configuring the Handling of the Switch

Three different functions in the microprocessor may operate the setting switches: Network Calls, Obstructs and the client request is being continued by the scheduler. We then discuss how the equipment screen continuously ensures the framework's safety by following the processor's configuration switch for

1) These interrupts: Intrudes are the primary regular drivers of setting exchanging. Since hinders occur non concurrently, the actual intrude on signal is introduced to both the processor and the observing equipment. The ISR checking chart is consistently occupant in observing diagram memory. On the off chance that the screen identifies an illicit guidance implementation during the ISR implementation, it rearranges the processor and it can choose for handicap intrudes. In this case, the CPU indicates that it should ignore IRQ strobes in the future by writing to a record on the screen.

Figure 2. Multi-context Computing System

Framework Calls: Another wellspring of setting exchanging is framework calls. Throughout the framework calls, the client's work is undecided until the working framework proceeds to manage back to it.

IJCM 5

Framework suggests are permitted with an a gestational for checking, and control over an observing diagram for the framework's operation is authorized. A field added to the client task observing chart for the executed advice determines the GID of the capacity when a client task invokes a framework job.

Operating system Scheduler: The operating system client task scheduler is the most well-known source of setting switches. The clock ISR activation is the source of the Operating scheduler's two typically continuous summonses, and the claim framework explains how to turn over the CPU. The scheduler selects the subsequent cycle to execute when it is summoned. Despite the possibility of collaboration or alternative approaches, a need-based scheduler is used in  $\mu$ C/OS-II. When the next undertaking is resolved, the processor advances the assignment's PID to the screen.

#### Recuperation

At the point when an assault is identified, the screen flags a rearrange to the processor. For function measures, the working framework can execute the cycle and utilize interior instruments to recuperate reminiscence and take up the relevance. Many implanted applications can recoup from such revive. On the off chance that important, more perplexing checkpointing and recuperation systems can be executed. On the off chance that the reset happens during the working framework preparing, at that point, the whole framework should be restarted.

#### 5. IMPLEMENTATION OF PROTOTYPE

We have built up a model usage of the equipment observing framework to demonstrate its viability in giving safety to implanted working frameworks and their uses.

#### Framework Setup and Attack Scenario

A new equipment screen is added to our framework, which consists of a basic NIOS II delicate processor. The Altera Stratix IV FPGA is used to implement the Verilog-depicted architecture on the Terasic DE4 FPGA device. The principle microprocessor and the system screen are co-situated within an additional NIOS II center that has a dedicated RSA decryption engine for private technology screen stacking in order to create new charts and parallels. Scrambled doubles and schematics via a compact disk are viewed by this cofound machine, which then unscrambles and verifies them before feeding them to the main engine and the equipment screen. A basic discussion of the doubles' and diagrams' protection setup may be found in [17].

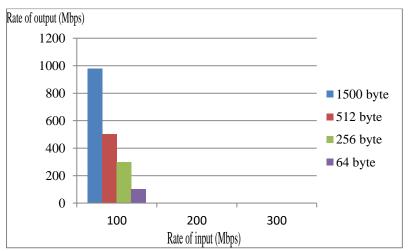

At the point when no assault packets are sent, the throughput of the organization processor framework increments and arrives at the greatest. At the point when assault parcels are incorporated the throughput arrives at the greatest, and afterward diminishes somewhat before settling down [18].

Figure 4. Performance of Network Processor with Various Packet Size

#### **Attack Detection**

Figure 3 shows the performance of the hardware network processor along with various packet sizes. The screen displays instructions that don't match the observing diagram of the request paired or working framework that is currently dynamic while the processor is being attacked and the assault code is being implemented. In particular, the adequate hashed esteems (0a pair of 0800, i.e., 11 of every instantaneous coding) and the publicly visible secret valued (0the value of x0008, i.e., 3 of every instantly coding) differ at phase 18. The reset instruction is therefore confirmed.

Although our safe packet processor's results are empowering because they show that there are safeguards against the types of attacks we describe in this thesis, it is important to emphasize that these

6

safeguards are not currently communicated on the Internet. Current programming-based switches are currently helpless, therefore more creative effort is needed to create and send defenses against this new type of attack.

|             | Benchmark     | Fixed    | Instructions | Graph entries | Graph size |

|-------------|---------------|----------|--------------|---------------|------------|

|             |               | Hardware | Count        |               |            |

| μC/OS-II    | IPv4 (1 core) | 6275     | 325          | 23,564        | 850,400    |

| bitcount    | CM (1 core)   | 6274     | 287          | 7,758         | 280,628    |

| qsort large | IPv4 (4 core) | 25086    | 325          | 9,201         | 328,104    |

| qsort small | CM (4core)    | 25086    | 287          | 9,123         | 325,955    |

Table 1. Utilization of Network Processor Benchmarks

We extracted the observation diagram for  $\mu$ C/OS-II and several benchmarks from [19] using the chart extraction method shown in. Small changes were made in order to run the benchmarks on our NIOS-based stage. For example, there is no record framework in our framework. Hence, we needed to utilize static predefined informational indexes as opposed to perusing from documents. All out guidelines and control stream directions (branches) are listed alongside the assets needed to fabricate the screens. Both the CM method and normal bundle transmission (IPv4) screens are included. While individual fixed rationale screens were necessary for four-center executions, programmable rationale screens were shared for four-center usage. The new methodology spares extensive square memory assets notwithstanding considering asset sharing between the screens [20].

#### 6. CONCLUSION

In outline, installed frameworks are especially powerless to assault. Their restricted assets don't permit the utilization of customary programming based protection systems. In this work, we introduced an equipment-based safety component that can guarantee the right implementation of uses and working framework code at the granularity of personality directions. Our model framework illustrates that the projected instrument is feasible for these profoundly unique conditions and successful in recognizing any assault, even those that were already obscure. We accept that this work provides a significant advance towards secure installed preparing frameworks for a wide scope of application areas.

#### REFERENCES

- [1] Arman Pouraghily, Tilman Wolf and Russell Tessier, "Hardware Support for Embedded Operating System Security", IEEE 2017.

- [2] Internet of Things: Privacy & Security in a Connected World, Federal Trade Commission, Jan. 2015.

- [3] D. E. Sanger and N. Perlroth, "A new era of internet attacks powered by everyday devices," The New York Times, Oct. 2016.

- [4] T. Jaeger, Ed., Operating System Security. Morgan and Claypool, 2008.

- [5] G. E. Suh, J. W. Lee, D. Zhang, and S. Devadas, "Secure program execution via dynamic information flow tracking," in ASPLOS-XI: Proceedings of the 11th international conference on Architectural support for programming languages and operating systems, Boston, MA, Oct.2004, pp. 85–96.

- [6] N. Vachharajani, M. J. Bridges, J. Chang, R. Rangan, G. Ottoni, J. A. Blome, G. A. Reis, M. Vachharajani, and D. I. August, "RIFLE: An architectural framework for user-centric information-flow security," in Proc. of 37th International Symposium on Microarchitecture, Portland, OR, Dec. 2004, pp. 243–254.

- [7] X. Zhai, K. Appiah, S. Ehsan, G. Howells, H. Hu, D. Gu, and K. D.McDonald-Maier, "Method for detecting abnormal program behavior on embedded devices," IEEE Transactions on Information Forensics and Security, vol. 10, no. 8, pp. 1692–1704, Aug. 2015.

- [8] A. Waksman and S. Sethumadhavan, "Tamper evident microprocessors," in Proc. of IEEE Symposium on Security and Privacy, Oakland, CA, May 2010, pp. 173–188.

- [9] R. Sekar, M. Bendre, D. Dhurjati, and P. Bollineni, "A fast automaton-based method for detecting anomalous program behaviors," in Proc. Of the IEEE Symposium on Security and Privacy, Oakland, CA, May 2001, pp. 144– 155.

- [10] D. Arora, S. Ravi, A. Raghunathan, and N. K. Jha, "Secure embedded processing through hardware-assisted runtime monitoring," in Proc. Of the Design, Automation and Test in Europe Conference and Exhibition (DATE'05), Munich, Germany, Mar. 2005, pp. 178–183.

- [11] S. Mao and T. Wolf, "Hardware support for secure processing in embedded systems," in Proc. of 44th Design Automation Conference (DAC), San Diego, CA, Jun. 2007, pp. 483–488.

- [12] K. Hu, H. Chandrikakutty, Z. Goodman, R. Tessier, and T. Wolf, "Dynamic hardware monitors for network processor protection," IEEE Transactions on Computers, vol. 65, no. 3, pp. 860–872, Mar. 2016.

IJCM □ 7

[13] T. Thomas, A. Pouraghily, K. Hu, R. Tessier, and T. Wolf, "Multi-task support for security-enabled embedded processors," in Proc. Of 26th IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), Toronto, ON, Jul. 2015, pp. 136–143.

- [14] H. Theiling, "Extracting safe and precise control flow from binaries," in Real-Time Computing Systems and Applications, 2000. Proceedings. Seventh International Conference on. IEEE, 2000, pp. 23–30.

- [15] H. Chandrikakutty, D. Unnikrishnan, R. Tessier, and T. Wolf, "High-performance hardware monitors to protect network processors from data plane attacks," in Design Automation Conference (DAC), 2013 50<sup>th</sup>ACM/EDAC/IEEE. IEEE, 2013, pp. 1–6.

- [16] S. Mao and T. Wolf, "Hardware support for secure processing in embedded systems," in Proc. of 44th Design Automation Conference (DAC), San Diego, CA, Jun. 2007, pp. 483–488.

- [17] C. Cowan, M. Barringer, S. Beattie, G. Kroah-Hartman, M. Frantzen, and J. Lokier, "FormatGuard: Automatic protection from printf format string vulnerabilities," in USENIX Security Symposium, Washington, DC, Aug. 2001.

- [18] Hu, Kekai, "Securing Network Processors with Hardware Monitors" (2015). Doctoral Dissertations. 516. https://scholarworks.umass.edu/dissertations\_2/516

- [19] M. R. Guthaus, J. S. Ringenberg, D. Ernst, T. M. Austin, T. Mudge, and R. B. Brown, "MiBench: A free, commercially representative embedded benchmark suite," in Proc. of IEEE 4th Annual Workshop on WorkloadCharacterization, Austin, TX, Dec. 2001.